# Organic Nonvolatile Memory Transistors for Flexible Sensor Arrays

Tsuyoshi Sekitani *et al.*Science **326**, 1516 (2009);

DOI: 10.1126/science.1179963

This copy is for your personal, non-commercial use only.

If you wish to distribute this article to others, you can order high-quality copies for your colleagues, clients, or customers by clicking here.

**Permission to republish or repurpose articles or portions of articles** can be obtained by following the guidelines here.

The following resources related to this article are available online at www.sciencemag.org (this information is current as of May 13, 2014):

**Updated information and services,** including high-resolution figures, can be found in the online version of this article at:

http://www.sciencemag.org/content/326/5959/1516.full.html

Supporting Online Material can be found at:

http://www.sciencemag.org/content/suppl/2009/12/10/326.5959.1516.DC1.html

This article cites 22 articles, 2 of which can be accessed free: http://www.sciencemag.org/content/326/5959/1516.full.html#ref-list-1

This article has been cited by 1 article(s) on the ISI Web of Science

This article has been **cited by** 6 articles hosted by HighWire Press; see: http://www.sciencemag.org/content/326/5959/1516.full.html#related-urls

This article appears in the following **subject collections**: Physics, Applied

http://www.sciencemag.org/cgi/collection/app\_physics

S. Guiriec, <sup>35</sup> Y. Hanabata, <sup>36</sup> A.K. Harding, <sup>21</sup> M. Hayashida, <sup>3</sup> E. Hays, <sup>21</sup> A. B. Hill, <sup>28</sup> L. Hjalmarsdotter, <sup>4,5</sup> D. Horan, <sup>17</sup> R. E. Hughes, <sup>12</sup> M. S. Jackson, <sup>5,37</sup> G. Jóhannesson, <sup>3</sup> A. S. Johnson, <sup>3</sup> T. J. Johnson, <sup>21,33</sup> W. N. Johnson, <sup>1</sup> T. Kamae, <sup>3</sup> H. Katagiri, <sup>36</sup> N. Kawai, <sup>38,39</sup> M. Kerr, <sup>18</sup> J. Knödlseder, <sup>42</sup> M. L. Kocian, <sup>3</sup> E. Koerding, <sup>7</sup> M. Kuss, <sup>6</sup> J. Lande, <sup>3</sup> L. Latronico, <sup>6</sup> M. Lemoine-Goumard, <sup>29,30</sup> F. Longo, <sup>8,9</sup> F. Loparco, <sup>15,16</sup> B. Lott, <sup>29,30</sup> M. N. Lovellette, <sup>1</sup> P. Lubrano, <sup>13,14</sup> G. M. Madejski, <sup>3</sup> A. Makeev, <sup>4,41</sup> L. Marchand, <sup>42</sup> M. Marelli, <sup>20</sup> W. Max-Moerbeck, <sup>43</sup> M. N. Mazziotta, <sup>16</sup> N. McColl, <sup>42</sup> J. E. McEnery, <sup>21,33</sup> C. Meurer, <sup>26,5</sup> P. F. Michelson, <sup>3</sup> S. Migliari, <sup>44</sup> W. Mitthumsiri, <sup>3</sup> T. Mizuno, <sup>36</sup> C. Monte, <sup>15,16</sup> M. E. Monzani, <sup>3</sup> A. Morselli, <sup>36</sup> I. V. Moskalenko, <sup>3</sup> S. Murgia, <sup>3</sup> P. L. Nolan, <sup>3</sup> J. P. Norris, <sup>46</sup> E. Nuss, <sup>24</sup> T. Ohsuqi, <sup>36</sup> N. Omodei, <sup>6</sup> R. A. Ong, <sup>42</sup> J. F. Ormes, <sup>6</sup> D. Paneque, <sup>3</sup> D. Parent, <sup>29,30</sup> V. Pelassa, <sup>24</sup> M. Pepe, <sup>13,14</sup> M. Pesce-Rollins, <sup>6</sup> F. Piron, <sup>24</sup> G. Pooley, <sup>47</sup> T. A. Porter, <sup>48</sup> K. Pottschmidt, <sup>21</sup> S. Rainò, <sup>15,16</sup> R. Rando, <sup>10,11</sup> P. S. Ray, <sup>1</sup> M. Razzano, <sup>6</sup> N. Rea, <sup>19,49</sup> A. Readhead, <sup>33</sup> A. Reimer, <sup>50,3</sup> O. Reimer, <sup>50,3</sup> J. L. Richards, <sup>43</sup> L. S. Rochester, <sup>3</sup> J. Rodriguez, <sup>7</sup> A. Y. Rodriguez, <sup>19</sup> R. W. Romani, <sup>3</sup> F. Ryde, <sup>37,5</sup> H. F.-W. Sadrozinski, <sup>48</sup> A. Sander, <sup>12</sup> P. M. Saz Parkinson, <sup>48</sup> C. Sgrò, <sup>6</sup> E. J. Siskind, <sup>51</sup> D. A. Smith, <sup>29,30</sup> P. D. Smith, <sup>12</sup> P. Spinelli, <sup>15,16</sup> J. -L. Starck, <sup>7</sup> M. Stevenson, <sup>43</sup> M. S. Strickman, <sup>1</sup> D. J. Suson, <sup>52</sup> H. Takahashi, <sup>36,11</sup> T. Tanaka, <sup>3</sup> J. B. Thompson, <sup>21</sup> L. Tibaldo, <sup>10,11,7</sup> J. A. Tomsick, <sup>53</sup> D. F. Torres, <sup>54,19</sup> G. Tosti, <sup>13,14</sup> A. Tramacere, <sup>3,55</sup> Y. Uchiyama, <sup>3</sup> T. L. Usher, <sup>3</sup> V. Vasileiou, <sup>22,23</sup> N. Vilchez, <sup>40</sup> V. Vitale, <sup>45,56</sup> A. P. Waite, <sup>3</sup> P. Wang, <sup>3</sup> J. Wilms, <sup>57</sup> B. L. Winer, <sup>12</sup> K. S. Wood, <sup>1</sup> T. Vliner, <sup>37,58,5</sup> M. Ziegler, <sup>48</sup>

<sup>1</sup>Space Science Division, Naval Research Laboratory, Washington, DC 20375, USA. <sup>2</sup>National Research Council Research Associate, National Academy of Sciences, Washington, DC 20001, USA. <sup>3</sup>W. W. Hansen Experimental Physics Laboratory, Kavli Institute for Particle Astrophysics and Cosmology, Department of Physics and SLAC National Accelerator Laboratory, Stanford University, Stanford, CA 94305, USA. <sup>4</sup>Department of Astronomy, Stockholm University, SE-106 91 Stockholm Sweden. <sup>5</sup>The Oskar Klein Centre for Cosmoparticle Physics, AlbaNova, SE-106 91 Stockholm, Sweden. <sup>6</sup>Istituto Nazionale di Fisica Nucleare, Sezione di Pisa, I-56127 Pisa, Italy. <sup>7</sup>Laboratoire AIM, CEA-IRFU/CNRS/Université Paris Diderot, Service d'Astrophysique, CEA Saclay, 91191 Gif sur Yvette, France. <sup>8</sup>Istituto Nazionale di Fisica Nucleare, Sezione di Trieste, Italy. <sup>9</sup>Dipartimento di Fisica, Università di Trieste, Italy. <sup>10</sup>Istituto Nazionale di Fisica Nu-

cleare, Sezione di Padova, I-35131 Padova, Italy. 11 Dipartimento di Fisica "G. Galilei," Università di Padova, I-35131 Padova, Italy. 12 Department of Physics, Center for Cosmology and Astro-Particle Physics, Ohio State University, Columbus, OH 43210, USA. <sup>13</sup>Istituto Nazionale di Fisica Nucleare, Sezione di Perugia, I-06123 Perugia, Italy. <sup>14</sup>Dipartimento di Fisica, Università degli Studi di Perugia, I-06123 Perugia, Italy. <sup>15</sup>Dipartimento di Fisica "M. Merlin" dell'Università e del Politecnico di Bari, I-70126 Bari, Italy. <sup>16</sup>Istituto Nazionale di Fisica Nucleare, Sezione di Bari, 70126 Bari, Italy, 17 Laboratoire Leprince-Ringuet, École polytechnique, CNRS/IN2P3, Palaiseau, France. <sup>18</sup>Department of Physics, University of Washington, Seattle, WA 98195-1560, USA. 19 Institut de Ciencies de l'Espai (IEEC-CSIC), Campus UAB, 08193 Barcelona, Spain. <sup>20</sup>INAF-Istituto di Astrofisica Spaziale e Fisica Cosmica, I-20133 Milano, Italy. <sup>21</sup>NASA Goddard Space Flight Center, Greenbelt, MD 20771, USA. <sup>22</sup>Center for Research and Exploration in Space Science and Technology (CRESST) and NASA Goddard Space Flight Center, Greenbelt, MD 20771, USA. <sup>23</sup>Department of Physics and Center for Space Sciences and Technology, University of Maryland Baltimore County, Baltimore, MD 21250, USA. <sup>24</sup>Laboratoire de Physique Théorique et Astroparticules, Université Montpellier 2, CNRS/ IN2P3. Montpellier, France. <sup>25</sup>Department of Physics and Astronomy, Sonoma State University, Rohnert Park, CA 94928-3609, USA. <sup>26</sup>Department of Physics, Stockholm University, AlbaNova, SE-106 91 Stockholm, Sweden. <sup>27</sup>Institut Universitaire de France, 75005 Paris, France. <sup>28</sup>Université Joseph Fourier-Grenoble 1/CNRS, Laboratoire d'Astrophysique de Grenoble (LAOG) UMR 5571, BP 53, 38041 Grenoble Cedex 09, France. <sup>29</sup>Université de Bordeaux, Centre d'Études Nucléaires Bordeaux Gradignan, UMR 5797, Gradignan, 33175, France. <sup>30</sup>CNRS/IN2P3, Centre d'Études Nucléaires Bordeaux Gradignan, UMR 5797, Gradignan, 33175, France. <sup>31</sup>Dipartimento di Fisica, Università di Udine and Istituto Nazionale di Fisica Nucleare, Sezione di Trieste, Gruppo Collegato di Udine, I-33100 Udine, Italy. <sup>32</sup>Department of Astronomy and Astrophysics, Pennsylvania State University, University Park, PA 16802, USA. 33 Department of Physics and Department of Astronomy, University of Maryland, College Park, MD 20742, USA. 34 Max-Planck-Institut für Radioastronomie, Auf dem Hügel 69, 53121 Bonn, Germany. 35Center for Space Plasma and Aeronomic Research (CSPAR), University of Alabama in Huntsville, Huntsville, AL 35899, USA. <sup>36</sup>Department of Physical Sciences, Hiroshima University, Higashi-Hiroshima,

Hiroshima 739-8526, Japan. 37Department of Physics, Royal Institute of Technology (KTH), AlbaNova, SE-106 91 Stockholm, Sweden. <sup>38</sup>Department of Physics, Tokyo Institute of Technology, Meguro City, Tokyo 152-8551, Japan. 39Cosmic Radiation Laboratory, Institute of Physical and Chemical Research (RIKEN), Wako, Saitama 351-0198, Japan. 40Centre d'Étude Spatiale des Rayonnements, CNRS/UPS, BP 44346, F-30128 Toulouse Cedex 4, France. <sup>41</sup>George Mason University, Fairfax, VA 22030, USA. <sup>42</sup>Department of Physics and Astronomy, University of California, Los Angeles, CA 90095-1547. USA. <sup>43</sup>Cahill Center for Astronomy and Astrophysics, California Institute of Technology, Pasadena, CA 91125, USA. <sup>44</sup>European Space Astronomy Centre (ESAC), 28691 Villanueva de la Cañada, Madrid, Spain. 45 Istituto Nazionale di Fisica Nucleare, Sezione di Roma "Tor Vergata", I-00133 Roma, Italy. 46Department of Physics and Astronomy, University of Denver, Denver, CO 80208, USA. 47 Cavendish Laboratory, Cambridge CB3 0HE, UK. 48 Santa Cruz Institute for Particle Physics, Department of Physics and Department of Astronomy and Astrophysics, University of California at Santa Cruz, Santa Cruz, CA 95064, USA. <sup>49</sup>Sterrenkundig Institut "Anton Pannekoek," 1098 SJ Amsterdam, Netherlands. 50 Institut für Astro- und Teilchenphysik and Institut für Theoretische Physik, Leopold-Franzens-Universität Innsbruck, A-6020 Innsbruck, Austria, 51NYCB Real-Time Computing Inc., Lattingtown, NY 11560-1025, USA. 52Department of Chemistry and Physics, Purdue University Calumet, Hammond, IN 46323-2094, USA. 53Space Sciences Laboratory, University of California, Berkeley, CA 94720, USA. <sup>54</sup>Institució Catalana de Recerca i Estudis Avançats (ICREA), Barcelona, Spain. <sup>55</sup>Consorzio Interuniversitario per la Fisica Spaziale (CIFS), I-10133 Torino, Italy. <sup>56</sup>Dipartimento di Fisica, Università di Roma "Tor Vergata," I-00133 Roma, Italy. 57 Erlangen Centre for Astroparticle Physics, D-91058 Erlangen, Germany. 58School of Pure and Applied Natural Sciences, University of Kalmar, SE-391 82 Kalmar, Sweden.

### Supporting Online Material

www.sciencemag.org/cgi/content/full/1182174/DC1 Materials and Methods Figs. S1 to S3 References

18 September 2009; accepted 5 November 2009 Published online 26 November 2009; 10.1126/science.1182174 Include this information when citing this paper.

# Organic Nonvolatile Memory Transistors for Flexible Sensor Arrays

Tsuyoshi Sekitani,<sup>1</sup> Tomoyuki Yokota,<sup>2</sup> Ute Zschieschang,<sup>3</sup> Hagen Klauk,<sup>3</sup> Siegfried Bauer,<sup>4</sup> Ken Takeuchi,<sup>1</sup> Makoto Takamiya,<sup>5</sup> Takayasu Sakurai,<sup>5</sup> Takao Someya<sup>1,2,6</sup>\*

Using organic transistors with a floating gate embedded in hybrid dielectrics that comprise a 2-nanometer-thick molecular self-assembled monolayer and a 4-nanometer-thick plasma-grown metal oxide, we have realized nonvolatile memory arrays on flexible plastic substrates. The small thickness of the dielectrics allows very small program and erase voltages (≤6 volts) to produce a large, nonvolatile, reversible threshold-voltage shift. The transistors endure more than 1000 program and erase cycles, which is within two orders of magnitude of silicon-based floating-gate transistors widely employed in flash memory. By integrating a flexible array of organic floating-gate transistors with a pressure-sensitive rubber sheet, we have realized a sensor matrix that detects the spatial distribution of applied mechanical pressure and stores the analog sensor input as a two-dimensional image over long periods of time.

Electronic devices are traditionally fabricated using inorganic semiconductors, rigid substrates, and high-temperature manufacturing methods. In contrast, organic semiconductors can be processed at low temperatures and on large-area polymeric substrates. This has allowed for the development of a variety of electronic devices on

flexible plastic substrates, including solar cells (1), light-emitting diode displays (2), field-effect transistors (3), transponders (4), sensors (5), actuators (6), and nonvolatile memory transistors (7–11). Nonvolatile memory transistors are potentially useful to individualize radio-frequency transponders or to store data obtained by large-area sensor arrays

for later read-out. Most of the organic memory transistors reported to date exploit the electric field-induced remnant polarization in ferroelectric polymer films (7–11). A considerable limitation of ferroelectric polymer memory transistors is that the coercive field required to reverse the macroscopic polarization increases with decreasing film thickness (12), which makes it difficult to obtain a large enough memory window with program and erase voltages below about 20 V. Also, due to the substantial surface roughness of the ferroelectric polymer films, the carrier field-effect mobility in these transistors is usually quite low (<0.1 cm<sup>2</sup>/Vs).

<sup>1</sup>Department of Electrical and Electronic Engineering and Information Systems, The University of Tokyo, 7-3-1 Hongo, Bunkyo-ku, Tokyo 113-8656, Japan. <sup>2</sup>Department of Applied Physics, The University of Tokyo, 7-3-1 Hongo, Bunkyo-ku, Tokyo 113-8656, Japan. <sup>3</sup>Max Planck Institute for Solid State Research, Heisenbergstrasse 1, 70569 Stuttgart, Germany. <sup>4</sup>Soft Matter Physics (SOMAP), Johannes Kepler University Linz, A-4040 Linz, Austria. <sup>5</sup>Institute of Industrial Science, The University of Tokyo, 4-6-1 Komaba, Meguro-ku, Tokyo 153-8505 Japan. <sup>6</sup>Institute for Nano Quantum Information Electronics (INQIE), The University of Tokyo, 4-6-1 Komaba, Meguro-ku, Tokyo 153-8505 Japan.

\*To whom correspondence should be addressed. E-mail: Someya@ee.t.u-tokyo.ac.jp.

A floating-gate transistor is a field-effect transistor with two gate electrodes. In addition to the control gate, similar to that in a regular transistor, it has a floating gate embedded in the gate dielectric. When the dielectric is thin enough, electronic charge can be brought onto the floating gate by quantum tunneling or thermal emission when a large enough program voltage is applied between

the control gate and the source contact. Charging the floating gate changes the transistor's threshold voltage, because the charge on the floating gate partially screens the electric field between the control gate and the semiconductor. This threshold voltage shift can be detected by measuring the drain current at a certain gate-source voltage. Because the floating gate is completely isolated by the di-

electric, charge stored on the floating gate remains there without the need for any applied voltage (nonvolatile memory). To erase the memory, a voltage of opposite polarity is applied, discharging the floating gate through the dielectric.

In silicon-based floating-gate transistors, the dielectric is a silicon dioxide layer with a thickness of a few nanometers. The exact thickness is a

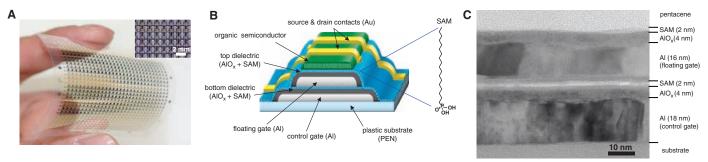

**Fig. 1.** (**A**) Photograph of an organic floating-gate transistor sheet comprising 26 by 26 memory cells. The array has an effective area of 50 by 50 mm<sup>2</sup>. The inset shows a magnified image of the array. (**B**) Schematic cross section of the floating-gate transistors. The substrate is flexible PEN. The control and floating gates are 20-nm-thick layers of evaporated aluminum. The top and bottom

dielectrics are each a combination of a 4-nm-thick layer of  ${\rm AlO}_{\rm x}$  and a 2-nm-thick SAM. The organic semiconductor is a 50-nm-thick layer of pentacene, and the source and drain contacts are 50-nm-thick layers of evaporated gold. (C) Cross-sectional TEM images of a flexible floating-gate transistor. The specimen was prepared using a focused ion beam and imaged by TEM (300 kV).

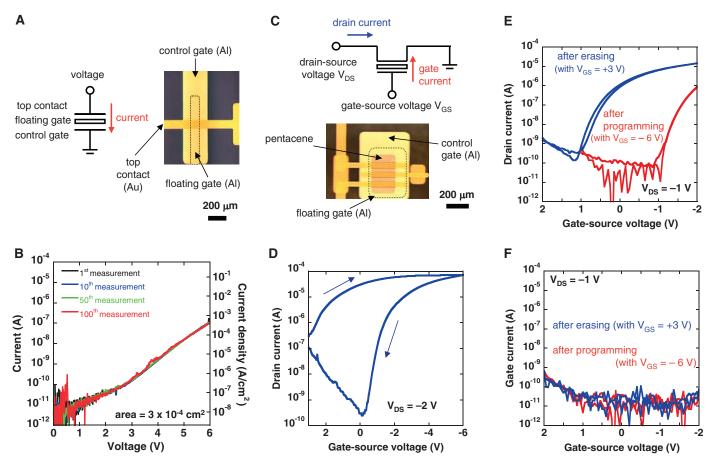

**Fig. 2.** Static electrical performance of the floating-gate memory devices. **(A)** Photograph of a floating-gate capacitor used for characterizing the voltage-dependent current through the AlO<sub>x</sub>/SAM dielectrics. **(B)** Current through the AlO<sub>x</sub>/SAM dielectrics as a function of applied voltage. Up to 6 V, the current does not cause irreversible changes in the dielectrics. **(C)** Photograph of a pentacene floating-gate memory transistor. **(D)** Drain current as a function of the voltage applied between control gate and source contact. When the

applied voltages are -6 V and +3 V, the floating gate is charged and discharged, causing a threshold-voltage shift and hysteresis in the current-voltage characteristics. (**E**) Read-out operation performed on a floating gate transistor after programming and after erasing for 1 s. The threshold-voltage shift induced by the program and erase operations is clearly observed. (**F**) Gate current of a floating-gate transistor measured during read-out. For read-out voltages up to  $\pm 2$  V, the gate current reaches about 100 pA.

compromise between the voltage required to bring enough charge onto the floating gate and the charge leakage from the floating gate, which sets an upper limit on the retention time. Silicon-based floatinggate transistors typically have program and erase

as electrode sheet

organic memory sheet

10 mm

voltages of 10 to 20 V (13, 14) and retention times of several years. Because the defect density in the thin dielectric increases with every program and erase operation, the endurance is usually limited to  $\sim 10^6$  program and erase cycles (14).

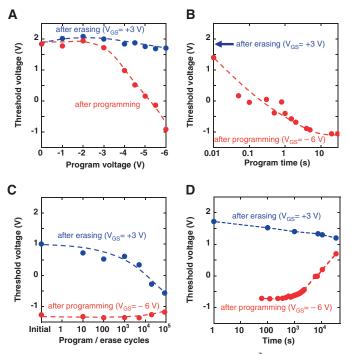

Fig. 3. Threshold voltage of organic floating-gate transistors. (A) Thresholdvoltage shift as a function of program voltage. The program voltage is applied for 1 s. At the maximum program voltage of -6 V, a threshold-voltage shift of about 2.5 V is obtained. The threshold voltage after erasing with +3 V is independent of the program voltage. (B) Thresholdvoltage shift as a function of the duration of the program pulse. The program voltage is -6 V. (C) Endurance of the memory transistors. The thresholdvoltage window is greater than 2 V after 10<sup>3</sup> program and erase (-6 to +3 V) cycles and greater than 1 V after 104 cycles. (D) Retention character-

istics of the memory transistors. The threshold voltage window is greater than 2 V after  $10^3$  s and greater than 1 V after 10<sup>4</sup> s. For each data point, the threshold voltage was obtained by measuring the complete transfer characteristics [sweeping gate-source voltage ( $V_{GS}$ ) from +2 to -2 V; drain-source voltage ( $V_{DS}$ ) = -1 V].

В

Although silicon floating-gate transistors are excellent for high-density data storage, flexible organic floating-gate transistors are potentially useful for large-area sensors and actuators with integrated nonvolatile memory capability. There are very few reports of organic floating-gate transistors, most of which use rigid substrates, thick dielectrics (10 to 50 nm) and large program and erase voltages (15 to 50 V), and none of which have demonstrated integration of these transistors into memory arrays (15-18). The main challenge in reducing the program and erase voltages and in demonstrating high yield and sufficient uniformity in large-area memory arrays on flexible plastic substrates is to develop a dielectric that can be prepared below the glass transition temperature of plastic film (<150°C) and which combines small film thickness with good reproducibility and small defect density. By taking advantage of the excellent properties of a lowtemperature hybrid dielectric based on a thin metal oxide and a self-assembled monolayer (SAM), we have developed flexible floating-gate transistors with small program and erase voltages (-6 V to +3 V). Figure 1A shows a photograph of a plastic sheet with 676 organic floating-gate transistors arranged in a 26 by 26 array on a 125-µmthick plastic film. The schematic device cross section is shown in Fig. 1B; the fabrication process is outlined in the Supporting Online Material. The two dielectrics that isolate the floating gate from the control gate and the organic semiconductor are a combination of a thin aluminum oxide (AlO<sub>x</sub>) layer grown in an oxygen plasma at room temperature and an alkyl-phosphonic acid SAM

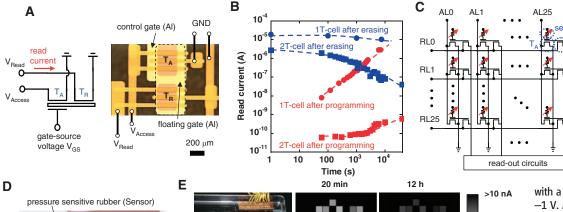

Fig. 4. Flexible pressuresensor array. (A) Schematic and photograph of a two-transistor (2T) memory cell in which an access transistor (TA) and a read-out transistor (T<sub>R</sub>) share a large floating gate. (B) Retention characteristics of a 2T cell in comparison with that of a 1T cell. The read current ( $I_{Read}$ ) is the drain current of T<sub>R</sub> measured

with a drain-source voltage ( $V_{Read}$ ) of -1 V. I<sub>Read</sub> depends on the threshold voltage of the transistors and thus on the amount of charge on the floating gate. (C) Circuit schematic of the sensor. Lines marked AL are the access lines used to apply a drain-source voltage of -2 V to the access transistors during program and erase operations. Lines marked RL are the read lines. The control gates of all access transistors are connected to the bottom surface of the pressure-sensitive rubber sheet. (D) Photograph of the

< 100 pA

three individual sheets before lamination. Bottom, 125-µm-thick PEN sheet with 676 2T memory cells; center, 500-µm-thick pressure-sensitive rubber sheet; top, 125-µm-thick PEN sheet with copper electrode. (E) Demonstration of the sensor array. The spatial distribution of mechanical pressure applied using two different objects is stored in the organic floating-gate transistors and can be retrieved even after the pressure and voltages have been removed.

prepared from solution at room temperature, with a total thickness of about 6 nm and a capacitance of 0.6 to 0.65  $\mu$ F/cm<sup>2</sup> (19–22). The semiconductor is a thin layer of vacuum-deposited pentacene.

Figure 1C shows a cross-sectional electron microscopy (EM) image of a completed device. The specimen was prepared using a focused ion beam (FIB) (FB-2100, Hitachi High-Technologies Corp., Tokyo, Japan) and imaged by transmission electron microscopy (TEM) (HF-3300 Cold-FE TEM, 300 kV, Hitachi High-Technologies Corp.). The control gate, the floating gate, and the two dielectric layers can be clearly distinguished in the TEM image. Perhaps most notably, the 2-nm-thick organic SAM of the bottom dielectric that separates the control gate from the floating gate is clearly resolved. The TEM image confirms the structure of the organic floating-gate transistors.

To characterize the electric current through the dielectrics during program and erase operations, floating-gate capacitors were prepared without the semiconductor (Fig. 2A). Figure 2B shows that when the voltage between the control gate and the top contact increases, the current also increases, reaching 0.5 mA/cm² at 6 V. This measurement was repeated 100 times without any changes in the current-voltage curves, showing that the dielectric can sustain this current. Beyond 6.3 V, however, an irreversible increase in current was observed, indicating damage to the dielectric (fig. S3A).

Figure 2C shows a photograph of a pentacene floating-gate memory transistor. Initially, the threshold voltage ( $V_{tb}$ ) is between +1 and +2 V (Figs. 2 and 3). For programming, a voltage of −6 V is applied between the control gate and the source contact. This creates a gate current of 1  $\mu A$ (fig. S3B), which charges the floating gate and shifts  $V_{th}$  to -1 V. To erase, a voltage of +3 V is applied to discharge the floating gate and recover the initial threshold voltage. Cycling the gate-source voltage between +3 V and -6 V produces the hysteresis seen in Fig. 2D. The exact  $V_{th}$  shift depends on the voltage and duration of the program pulse (Fig. 3, A and B, and figs. S4 and S5). To read the stored information,  $V_{\rm th}$  is determined, for example, by measuring the drain current as a function of gate-source voltage. Figure 2E shows the result of two read-out operations, one on a transistor programmed at -6 V, the other on a transistor erased at +3 V. The threshold voltage window and the device-to-device uniformity (fig. S6) are sufficient for unambiguous read-out. Figure 2F shows that if read-out is performed with a gate-source voltage of ±2 V, the gate current reaches 100 pA. This causes a small portion of the stored charge to be lost and  $V_{th}$  to shift slightly during each read-out operation (destructive read-out) (fig. S7, A and B). In contrast, if read-out is performed with a gatesource voltage of 0 V, there is no charge loss and no  $V_{\rm th}$  shift (nondestructive read-out) (fig. S7C).

Modern silicon-based flash memory is typically rated for  $10^6$  program and erase cycles (14), after which the memory characteristics degrade. To evaluate the endurance of the organic memory transistors, a device was subjected to  $10^5$

program and erase cycles (-6 V to +3 V, 1 Hz). The results in Fig. 3C and in fig. S8 show that the threshold voltage window is constant at 2 V up to 10<sup>3</sup> cycles. Beyond that, the positive threshold voltage shift during the erase operation becomes smaller, so the initial threshold voltage of +1 V is no longer recovered and the threshold voltage window becomes smaller. Nonetheless, after 10<sup>4</sup> cycles, the threshold voltage window is still 1 V, sufficient for unambiguous read-out. After 10<sup>5</sup> cycles, the threshold voltage window is 0.5 V. Interestingly, the initial threshold voltage of +1 V can be recovered by annealing the transistors at 140°C in dry nitrogen, which suggests that the endurance is limited not by irreversible structural damage but by reversible carrier trapping.

Unlike dynamic random access memory (DRAM), nonvolatile memories retain information in the absence of external voltages. In floatinggate transistors, this requires that the charge on the floating gate is prevented from leaking away through the dielectric. Data retention experiments on an individual pentacene device (shown in Fig. 3D) suggest that the retention time is only a few hours (threshold voltage window is 1.1 V after 3 hours, 0.6 V after 12 hours). However, most of the charge loss in this case occurred during readout. To improve retention, we have therefore designed and fabricated a two-transistor memory cell in which an access transistor (with control gate) and a read-out transistor (without control gate) share a floating gate with an area of 400 by 1000 μm<sup>2</sup> (Fig. 4A). Read-out is performed with a drain-source voltage of -1 V applied to the read-out transistor for 0.1 s or less, with no voltage applied on the control gate. This resulted in a significant improvement in retention time: After 3 hours, the read-current ratio is less than 2 for the one-transistor cell, but  $2 \times 10^2$  for the two-transistor cell. After 12 hours, the two-transistor cell still has a usably large read-current ratio of 10<sup>2</sup> (Fig. 4B).

To demonstrate the potential of organic floating-gate transistors and the two-transistor memory cell design, we fabricated a large-area flexible sensor that measures the spatial distribution of mechanical pressure applied to it and retains this data for more than 12 hours after the pressure and voltages have been removed. The sensor was fabricated by laminating three sheets: a polyethylene naphthalate (PEN) sheet with 676 two-transistor memory cells arranged in a 26 by 26 array, a pressure-sensitive rubber sheet, and a PEN sheet with a copper electrode. The circuit schematic is shown in Fig. 4C, a photograph of the three individual sheets before lamination is shown in Fig. 4D, photographs of the memory array are shown in fig. S10A, and a cross section of the laminated stack is shown in fig. S10B. The control gates of all 676 memory cells are connected to the bottom surface of the rubber sheet, and the top surface of the rubber sheet is in contact with the copper electrode. When mechanical pressure is applied to the rubber sheet, the electrical resistance between the rubber's top and bottom surfaces decreases (fig. S10C). By applying a program voltage to the copper electrode and an access voltage to all memory cells, the copper electrode supplies the program voltage to the floating-gate transistors in those positions where pressure is applied, and the pressure distribution is stored in the memory array.

Figure 4E shows a demonstration of the sensor. Pressure was applied using two different objects: a roll of tape and two fingers. The stored information was read out after 20 min and again after 12 hours with a multichannel drive system. As can be seen, the contrast between the programmed cells and the background deteriorates over time due to charge loss (Fig. 4B), but even 12 hours after removing the mechanical pressure and the electric voltages, the stored information showing the spatial distribution of the applied pressure was still successfully recovered.

#### **References and Notes**

- 1. D. Gebeyehu et al., Synth. Met. 118, 1 (2001).

- 2. L. Zhou et al., Appl. Phys. Lett. 88, 083502 (2006).

- 3. G. H. Gelinck et al., Nat. Mater. 3, 106 (2004).

- 4. P. F. Baude et al., Appl. Phys. Lett. 82, 3964 (2003).

- 5. T. Someya *et al.*, *Proc. Natl. Acad. Sci. U.S.A.* **102**, 12321 (2005)

- 6. T. Sekitani et al., Nat. Mater. 6, 413 (2007).

- C. A. Nguyen, S. G. Mhaisalkar, J. Ma, P. S. Lee, Org. Electron. 9, 1087 (2008).

- K. H. Lee, G. Lee, K. Lee, M. S. Oh, S. Im, Appl. Phys. Lett. 94, 093304 (2009).

- 9. T. Sekitani *et al.*, *IEEE Trans. Electron. Dev.* **56**, 1027 (2009).

- R. Schroeder, L. A. Majewski, M. Grell, Adv. Mater. 16, 633 (2004).

- 11. R. C. G. Naber et al., Nat. Mater. 4, 243 (2005).

- H. Kliem, R. Tadros-Morgane, J. Phys. D Appl. Phys. 38, 1860 (2005).

- 13. K. Takeuchi, IEEE J. Solid-State Circuits 44, 1227 (2009).

- R. Bez, E. Camerlenghi, A. Modelli, A. Visconti, *Proc. IEEE* 91, 489 (2003).

- 15. Z. Liu, F. Xue, Y. Su, Y. M. Lvov, K. Varahramyan, *IEEE Trans. NanoTechnol.* **5**, 379 (2006).

- L. Zhen, W. Guan, L. Shang, M. Liu, G. Liu, J. Phys. D Appl. Phys. 41, 135111 (2008).

- 17. W. Wang, J. Shi, D. Ma, *IEEE Trans. Electron. Dev.* **56**, 1036 (2009).

- 18. M.-F. Chang, P.-T. Lee, S. P. McAlister, A. Chin, *Appl. Phys. Lett.* **93**, 233302 (2008).

- 19. H. Klauk, U. Zschieschang, J. Pflaum, M. Halik, *Nature* **445**, 745 (2007).

- 20. H. Ma et al., Appl. Phys. Lett. 92, 113303 (2008).

- T. Sekitani, Y. Noguchi, U. Zschieschang, H. Klauk, T. Someya, Proc. Natl. Acad. Sci. U.S.A. 105, 4976 (2008).

- 22. P. H. Wöbkenberg et al., Appl. Phys. Lett. 93, 013303 (2008).

- 23. This study was partially supported by Core Research for Evolutional Science and Technology, Japan Science and Technology Agency (JST/CREST), Global Centers of Excellence (GCOE, Secure-Life Electronics, University of Tokyo), and the Special Coordination Funds for Promoting and Technology. We thank H. Matsumoto and Y. Kuroda (Hitachi High-Technologies Corp.) for the process using FIB and imaging by TEM, H. Takagi (GENESIS Co., Ltd.) for designing the multichannel sensor driving system, and Daisankasei Co., Ltd. for high-purity parylene (diX-SR). We also thank T. Furukawa (Tokyo University of Science) and R. Koeppe (Johannes Kepler University Linz) for valuable discussion. S.B. thanks the Austrian Science Funds for financial support.

## Supporting Online Material

www.sciencemag.org/cgi/content/full/326/5959/1516/DC1 Materials and Methods SOM Text

Figs. S1 to S10

31 July 2009; accepted 23 October 2009 10.1126/science.1179963